## Demonstration of Monolithic Co-fabrication of Y1Ba2Cu3O7-δ and CMOS Devices on the Same Sapphire Substrate

P.R. de la Houssayea, M.J. Burnsb, W.J. Rubyb, S.D. Russella, S.R. Claytona, G.A. Garciaa, L.P. Leeb

a NCCOSC RDTE DIV (NRaD) 553, 49375 Ashburn Rd. Rm 2, San Diego, CA 92152-7633 b Conductus, Inc., 969 W. Maude Ave., Sunnyvale, CA 94086

We report the first fabrication of active semiconductor and high temperature superconducting (HTS) devices on the same substrate. Complementary Metal-Oxide-Semiconductor (CMOS) transistors were fabricated on the same sapphire substrate as either YBCO flux-flow transistors (FFTs) or YBCO superconducting quantum interference devices (SQUIDs). All devices functioned as expected at 77 K without degradation, demonstrating

that a compatible process has been found to monolithically integrate adjacent CMOS and HTS devices.

In the seven years since the discovery of high-temperature superconductivity, the field of superconductive electronics has undergone explosive development. Due to difficulties in growing films directly on silicon, copper and oxygen contamination of the silicon layers during growth, and the high temperature environments seen in HTS growth, it has not been fully integrated with semiconductor based technology. Research has been focused on the use of superconducting interconnects between integrated circuits, which could lower chip power dissipation, reduce necessary interconnect width and pitch, and reduce dispersive loss. Several attempts have been made to fabricate HTS circuits or devices directly on Si or other semiconductor surfaces<sup>1,2</sup>; these layers were of low quality and were stress limited, and no devices were fabricated in the layers.

CMOS thin-film silicon on sapphire (SOS) devices utilizing improved silicon films have achieved performance equal to or better than bulk CMOS devices<sup>3</sup>. For low temperature, low power operation, CMOS SOS has a number of advantages over other silicon technologies<sup>4</sup>. Additionally, one of the best substrates for

growth of YBCO layers for superconducting devices is sapphire.

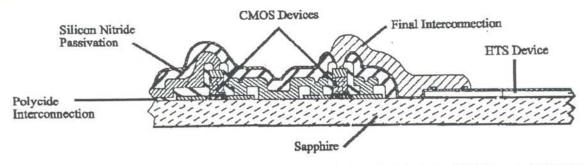

Fabrication of the thin-film SOS CMOS on sapphire was performed first. Further details relating to the CMOS processing in SOS can be found in Offord<sup>3</sup>. Areas that were to later have HTS devices were initially protected from various silicon processing steps such as high energy ion implants by initially not removing the silicon layer from the area. In CMOS circuit fabrication, a layer of aluminum is typically used as the interconnect layer between devices. Aluminum, however, cannot withstand the processing temperatures incumbent in superconducting device fabrication. For short distances, this layer was replaced by a second polycide (TiSi2) layer. After CMOS processing was complete, the silicon protective coating was removed in the HTS area and a 200 nm layer of Si<sub>3</sub>N<sub>4</sub> was deposited and patterned over the CMOS devices as a final passivating layer against the oxygen plasma and copper environments seen during the YBCO growth.

YBCO devices were then fabricated on the bare sapphire adjacent to the test CMOS devices, aligned lithographically. Pulsed laser deposition (PLD) techniques were used<sup>5</sup> in conjunction with a series of buffer layers<sup>6</sup>. For the production of grain-boundary SQUIDs, these buffer layers include final MgO and CeO layers used to produce a 45° in-plane rotation where desired. YBCO deposited over the Si3N4 regions was not superconducting. An amorphous Al2O3 layer was used as a passivation of the YBCO devices. Openings for electrical contact to both the YBCO devices and the CMOS can be made using photolithography and RIE or ion

milling and a final layer of metal can easily be patterned for a final interconnection layer.

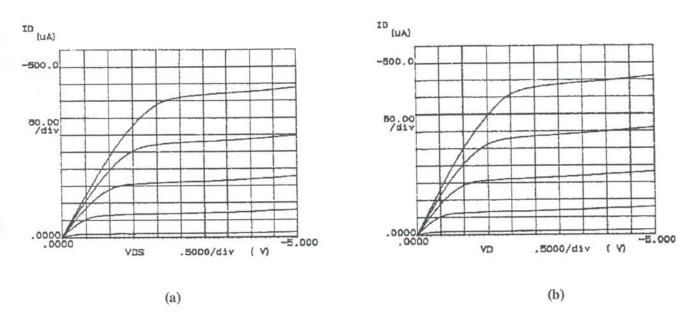

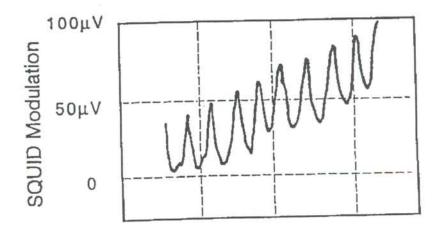

Both bi-epitaxial and step edge SQUIDs were made with modulation voltages at 77 K as large as 40 μV/F<sub>0</sub>. I-V curves from both p- and n-MOS devices were measured and compared with devices which did

not receive HTS processing. No significant difference was seen.

This demonstration opens up numerous other possibilities to explore the combination of these two well developed technologies. Circuits and devices that exploit the advantages of both HTS materials and SOS CMOS in order to mitigate the deficiencies of the other can be integrated together. For example, ultra-sensitive SQUIDs, bolometers, and ultra-high speed Flux-Flow Transistors and Josephson Junction based circuits (functioning at speeds of 100 GHz or more) can be combined with CMOS memories, latches, low noise amplifiers, silicon based sensors, and driving electronics.

<sup>&</sup>lt;sup>1</sup> D.K. Fork, D.B. Fenner, R.W. Barton, J.M. Philips, G.A.N. Connell, J.B. Boyce, T.H. Geballe. Appl. Phys. Lett., 57, 1161,

<sup>&</sup>lt;sup>2</sup> D.K. Fork, K. Nashimoto, T.H. Geballe. *Appl. Phys. Lett.*, **60**, 1621, 1991.

<sup>3</sup> B.W. Offord. 4th NASA Symposium on VLSI Design 1992, University of Idaho, October 29-30, 1992.

<sup>4</sup> M. Roser, S.R. Clayton, P.R. de la Houssaye, G.A. Garcia. Presented at 50th DRC, 1992.

<sup>5</sup> K. Char, M.S. Colclough, S.M. Garrison, N. Newman and G. Zaharchuk. *Appl. Phys. Lett.* **59**, 733 (1991). <sup>6</sup>L.P. Lee, K. Char, M.S. Colclough, and G. Zaharchuk. Appl. Phys. Lett. 59, 3051 (1991).

Figure 1. Cross-sectional Schematic View of Monolithically Co-fabricated HTS and CMOS Devices

Figure 2.  $3\mu m \times 20\mu m$  PMOS I-V Curves at 300K (a) Before and (b) After Co-fabrication

Figure 3. Functional Step-edge SQUID Monolithically Co-fabricated on CMOS/SOS